## ЭЛЕКТРОННЫЕ СРЕДСТВА: ИССЛЕДОВАНИЯ, РАЗРАБОТКИ

позволяет установить однозначное соответствие между объектами логико-информационной модели — алгоритмами, фрагментами алгоритмов и их информационно-кодовыми представлениями на всех уровнях иерархической системы, какой представляется проектируемое устройство.

Верификация разработанных блоков в реальной среде осуществляется с помощью программного комплекса, который включает в себя драйвер устройства, библиотеку функций для работы с драйвером, программу с модулями для верификации каждого блока в отдельности. При этом существенным достоинством программы является отображение векторов значения в форматах в двоичной и шестнадцатеричной форме, что позволяет использовать эти значения в системе моделирования ModelSim, которая отображает число с плавающей точкой только в виде вектора значения.

Верификация и тестирование разработанных функциональных блоков подтвердили корректную работу блоков, которые могут быть использованы любыми пользователями в своих проектах в виде готовых IP-Core.

#### ИСПОЛЬЗОВАННЫЕ ИСТОЧНИКИ

- 1. Estrin G. Organization of computer system: the fixed plus variable structure computer // Proc. Western Joint Computer Conf.— 1960.— N 5.— P. 33—40.

- 2. Микропроцессорные системы обработки информации / А. В. Палагин, Е. Л. Денисенко, Р. И. Белицкий, В. И. Сигалов.— К.: Наук. думка, 1993.

- 3. Cosoroaba A., Rivoallon F. Achieving higher system performance with the virtex-5 family of FPGAs / Xilinx Inc., White Paper WP245 (v1.1), May 17, 2006 / Available at http://www.xilinx.com.

- 4. Палагин А. В. Перспективы развития и вопросы теории проектирования микропроцессоров и микроЭВМ // УСиМ.— 1982.— № 3.— С. 24—29.

- 5. Палагин А. В., Опанасенко В. Н. Реконфигурируемые вычислительные системы.— К.: Просвіта, 2006.

- 6. Сергиенко И. В., Шило В. П. Задачи дискретной оптимизации. Проблемы, методы решения, исследования.— К.: Наук. думка, 2003.

- 7. Палагин А. В., Опанасенко В. Н., Лисовый А. Н. Проектирование реконфигурируемых систем на ПЛИС / Тр. Науч.-практич. конф. «СИЭТ-2006». Т. 1.— Одесса.— 2006.— С. 164.

- 8. Солдатов В. П. Программирование драйверов Windows.— М.: ООО «Бином-Пресс», 2004.

Д. т. н. В. Л. КОСТЕНКО, С. О. ЖАРОВЦЕВ

Украина, Одесский национальный политехнический университет E-mail: staz@normaplus.com

Дата поступления в редакцию 06.10 2006 г. — 14.02 2007 г. Оппонент *А. И. РАДКЕВИЧ* (НИИ микроприборов, г. Киев)

# МНОГОКАНАЛЬНОЕ ВЫСОКОТОЧНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ НЕЙРОЧИПОМ

Предложено многоканальное высокоточное устройство управления нейрочипом, позволяющее минимизировать

погрешность при формировании значений весовых коэффициентов синапсов и

расширить диапазон их рабочих значений.

Современные нейрочипы строятся на основе сложных многонейронных сетей, использующих комбинированную технологию, основанную на применении в одном нейрочипе цифровых и аналоговых схем [1], в состав которых входят нейроны, матрица связей, схемы обучения и восстановления, АЦП и ЦАП. В настоящее время для универсализации нейрочипов и повышения гибкости их нейросетей используют синапсы, обеспечивающие значения весовых коэффициентов в широком диапазоне. Поэтому минимальная погрешность, внесенная в значение весового коэффициента при его формировании, приведет к значительному снижению точности вычислений. Следовательно, актуальными представляются исследования возможности минимизации погрешности при формировании значений весовых коэффициентов синапсов.

Необходимо учитывать также, что при разработке нейрочипа задачу повышения производительности нельзя отрывать от задачи снижения погрешности преобразования и точности задания значений весовых коэффициентов.

Известно, что для миниатюризации нейрочипа применяются внешние устройства управления [1]. Такие устройства позволяют не только задавать и восстанавливать значения весовых коэффициентов, но и обучать нейросеть. Однако применение таких устройств для управления матрицей синапсов нейросетей ограничено быстродействием выходного элемента.

Известны устройства формирования временных интервалов коммутационного типа, позволяющие уменьшить паразитную задержку, возникающую в тракте преобразования при формировании среза задающего импульса [2, 3].

Задача исследований состояла в минимизации погрешности значений весовых коэффициентов за счет оптимизации выходных элементов, согласования выходного сигнала с входами нейрочипа, снижения временной задержки при формировании среза задающих импульсов.

На основе анализа принципов построения известного многоканального формирователя задающих импульсов нами установлено, что минимум паразитной временной задержки, которая определяется суммой переходных процессов последовательно соединенных электронных блоков в тракте преобразования, достигается за счет включения двухступенчатой памяти на базе Т-триггера и Д-триггера с динамическим син-

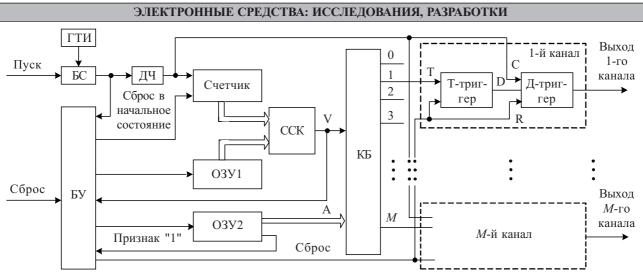

Рис. 1. Структурная схема многоканального высокоточного устройства формирования задающих импульсов

хровходом на каждый выход коммутатора [2]. Поэтому величина задержки значительно зависит от метрологических характеристик последнего элемента. Нами для дальнейшего повышения точности формирования в качестве выходного элемента предложен Д-триггер с потенциальным синхровходом (рис. 1), что позволило не менее чем в 2 раза снизить паразитную задержку.

Структурная схема предложенного многоканального формирователя состоит из кварцевого генератора тактовых импульсов (**ГТИ**), блока синхронизации (**БС**), делителя частоты (**ДЧ**), двоичного счетчика, адресных оперативных запоминающих устройств (**ОЗУ**1, ОЗУ2), блока управления (**БУ**), схемы сравнения двоичных кодов времени (**ССК**), коммутирующего блока (**КБ**), M каналов формирования фронтов задающих импульсов.

Отличительной особенностью схемы в сравнении с известными схемами линейных многоканальных формирователей коммутаторного типа является алгоритм его функционирования, а также включение двухступенчатой памяти на каждый выход коммутатора. Временные диаграммы работы приведены на рис. 2. Двухступенчатая память состоит из двух последовательно включенных Т- и Д-триггеров с потенциальным синхровходом. При этом синхровходы Д-триггеров объединены и включены в цепь "выход делителя частоты — вход счетчика".

Формирователь задающих импульсов выполнен на основе метода суммирования единичных временных приращений [2], при котором уменьшение динамической погрешности достигается преобразованием кода во фронт задающего импульса в два этапа, но за один такт работы ГТИ. На первом этапе формируется фронт задающего импульса, соответствующий коду, уменьшенному на единицу, с запоминанием этого фронта в первых триггерах двухступенчатой памяти заданных каналов. На втором этапе происходит перезапись информации из первых триггеров во вторые триггеры фронтом импульса ГТИ с одновременным формированием фронта временного интервала на выходах формирователя, отвечающего заданному коду. Сигналами установки в "1" и "Сброс" обеспе-

чивается соответственно установка в "единицу" всех триггеров суммирующего счетчика и сброс в "0" элементов всех каналов. В ОЗУ1 записываются двочиные коды длины импульсов в порядке возрастания, исключая код числа "нуль". В ОЗУ2 записываются группы двоичных кодов номеров каналов, причем коды в группе записываются в произвольном порядке, а последнему коду группы присваивается признак "1". При этом кварцевый ГТИ формирует непрерывную последовательность прямоугольных импульсов эталонной частоты.

Так как ОЗУ1 и ОЗУ2 разобщены в пространстве, то при записи информации в них группы кодов номеров каналов ставятся в однозначное соответствие кодам длин импульсов. Причем алгоритм работы цифрового утройства сравнения кодов неординарен и отличается от алгоритма работы классического ССК.

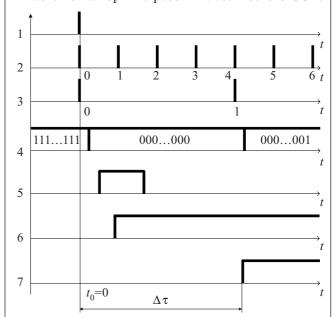

Рис. 2. Временные диаграммы работы устройства управления нейрочипом:

— Пуск: 2 — выход ГТИ: 3 — выход ЛЧ: 4 — двоичный код

I — Пуск; 2 — выход ГТИ; 3 — выход ДЧ; 4 — двоичный код на выходе счетчика; 5 — выход ССК; 6 — выход Т-триггера; 7 — выход Д-триггера; 2 — временная задержка тракта преобразования

## ЭЛЕКТРОННЫЕ СРЕДСТВА: ИССЛЕДОВАНИЯ, РАЗРАБОТКИ

Суть его работы сводится к следующему. Поступающий на вторые входы ССК программный код длины импульса уменьшается на единицу. Этот код сравнивается с соответствующим по величине кодом реальной длины импульса, сформированным счетчиком. В момент равенства кодов на обоих входах ССК на его выходе происходит смена потенциала, т. е. фиксируется результат сравнения; последний удерживается до момента изменения величины обоих или одного из кодов.

Как видно из рис. 2, момент начала работы многоканального высокоточного устройства формирования задающих импульсов определен моментом поступления сигнала "Пуск". Происходит сравнение кодов, при этом сигналом "Сравнение", полученным на выходе ССК, обеспечивается последовательное считывание обоих кодов номеров каналов первой группы с дальнейшим их распределением посредством блока коммутации и запоминанием в первых Т-триггерах двухступенчатой памяти каналов. То есть на предшествующем такте ДЧ обеспечивается предварительное преобразование и запоминание программного кода длины импульса, уменьшенного на единицу блоком ССК. С последующим импульсом ДЧ, отвечающим программному выходному коду длины импульса, происходит формирование фронтов задающих импульсов одновременно на всех выходах. Также следует отметить, что импульс ДЧ одновременно является и информационным по отношению к программному коду длины импульса и по отношению к Д-триггерам каналов. Коэффициент деления ДЧ выбирается следующим образом: если по максимуму, то он равен числу каналов устройства, если по минимуму, то коэффициент равен максимальному числу каналов, в которые одновременно (синхронно) планировалось бы формирование одного двоичного кода длины импульса.

В разработанном устройстве синхровходы триггеров второй ступени памяти каналов тракта формирования фронта задающего импульса объединяются и подключаются к суммирующему входу счетчика. Счетчик преобразует входной код в реальные параллельные позиционные двоичные коды длин импульсов. При этом стабильность фронта задающего импульса на выходе формирователя определена, в первую очередь, стабильностью выходных параметров синхронизируемой второй ступени памяти тракта формирования фронта задающего импульса. Одновременно на его синхровход поступает фронт высокостабильного импульса кварцевого ГТИ, выполняющего роль эталона времени. В аппаратных трактах формирования фронта задающего импульса в качестве первой ступени памяти выступает Т-триггер, а в качестве второй — Д-триггер с потенциальным синхровходом.

Признак «1» через блок управления, во-первых, останавливает чтение информации из ОЗУ2, а во-вторых, позволяет считывать очередной программный код времени из ОЗУ1, при этом, естественно, анализируется сигнал сравнения на выходе ССК. Такой алгоритм преобразования программных кодов во фрон-

ты задающих импульсов на протяжении цикла преобразования остается неизменным. Максимальное время цикла преобразования определяется количеством кодовых комбинаций счетчика и, естественно, не должно быть меньше количества программных кодов длин импульсов, предварительно записанных в ОЗУ1.

Необходимо отметить, что уменьшение  $\Delta \tau_i$  в формирователях адекватно достижению цели по повышению точности преобразования, т. е. снижению потерь информации в процессе преобразования.

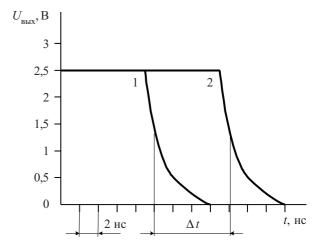

Был построен макет на микросхемах серии К555. Получен результат снижения временной задержки на 8—10 нс (рис. 3). Для снижения массогабаритных показателей в качестве Т- и Д-триггеров был применен ЈК-триггер. Исследована также возможность изготовления этого устройства на основе многоразрядных регистров с защелкиванием информации и разрешением выхода. Соответствующее уменьшение временной задержки наблюдалось и при использовании более быстродействующей элементной базы. Перечень элементов макета устройства на 32 канала приведен в таблице.

Рис. 3. Срезы сформированных импульсов: I — с двухступенчатой памятью; 2 — без двухступенчатой памяти

Перечень элементов

| Наименование элемента     | Количество элементов, шт. |

|---------------------------|---------------------------|

| Микросхема К555ЛН1        | 4                         |

| Микросхема К555РУ2        | 2                         |

| Микросхема К555ИЕ7        | 2                         |

| Микросхема К555ИЕ6        | 1                         |

| Микросхема КР531ТВ9       | 32                        |

| Микросхема К555ИМ3        | 2                         |

| Микросхема К555ЛЛ1        | 32                        |

| Микросхема К555ЛИ1        | 16                        |

| Резистор МЛТ-1-1,2 кОм    | 2                         |

| Резистор МЛТ-1-1,2 кОм    | 32                        |

| Конденсатор КМ-5б-0,1 мкФ | 32                        |

| Конденсатор КМ-5б-510 пкФ | 2                         |

| Конденсатор К53-100 мкФ   | 2                         |

## ЭЛЕКТРОННЫЕ СРЕДСТВА: ИССЛЕДОВАНИЯ, РАЗРАБОТКИ

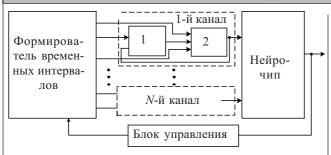

Рис. 4. Функциональная схема устройства управления нейрочипом:

*1* — Т-триггер; *2* — Д-триггер

Значительный интерес представляет также использование вместо микросхем серии К555 быстродействующих ПЛИС. Это позволит уменьшить время задержки и габариты исследуемого устройства.

Компьютерное моделирование, проведенное в программном пакете OrCAD Capture, также подтвердило, что устройство управления матрицей синапсов нейрочипа с предложенными нами выходными цифровыми блоками уменьшает временную задержку при формировании среза задающего импульса в 1,5—2 раза по сравнению с известными схемами [2].

На рис. 4 представлена функциональная схема подключения разработанного устройства к управляемому нейрочипу, из которой видно, что блок управления по результатам вычислений нейрочипа задает новое значение весовых коэфициентов синапсов через разработанный формирователь импульсов.

#### Выводы

Разработанное устройство управления нейрочипом позволяет устранить временные задержки, возникающие в процессе преобразования цифрового кода во фронт задающего импульса синхронно на выходах ряда определенных каналов. Устранение погрешности (по причине уменьшения временной задержки) и расширение функциональных возможностей разработаного устройства осуществляется за счет структурной схемы сравнения.

Использование разработанного многоканального высокоточного формирователя уменьшает время задержки, что позволяет снизить — по сравнению с классическими формирователями — инструментальную динамическую погрешность в 1,5—2 раза при формировании задающего импульса по одному или одновременно по ряду каналов.

К достоинствам описанного технического решения относится также то, что предложенный подход позволяет наиболее эффективным способом наращивать вычислительные возможности нейрочипа, тем самым увеличивая количество и сложность решаемых задач.

#### ИСПОЛЬЗОВАННЫЕ ИСТОЧНИКИ.

- 1. Галушкин А. И. Нейрокомпьютеры. Кн. 3. (Нейрокомпьютеры и их применение.).— М.: ИПРЖР, 2000.

- 2. Гитис Э. И., Пискулов Е. А. Аналогово-цифровые преобразователи.— М.: Энергоиздат, 1981.

- 3. Николенко И. Н. Многоканальный формирователь временных интервалов высокой точности // Тр. Одес. политехн. ун-та.— 1999.— Вып. 2 (8).— С. 150—153.

# НОВЫЕ КНИГИ

# Медведев А. Печатные платы. Конструкции и материалы.— М.: Техносфера, 2005.— 304 с.

Электроника — наиболее быстро развивающаяся область науки и техники, одно поколение сменяет другое каждые три-пять лет. Меняются и технологии печатных плат, сборки и монтажа компонентов, составляющих основу печатного монтажа. Базовые технологии печатных плат обрастают новыми приемами и операциями, расширяются их возможности за счет использования прецизионного оборудования, более качественных материалов.

В книге описаны схемы процессов, системы совмещений, технологии формирования топологического рисунка.

Монография предназначена как для технологов, работающих на производстве печатных плат, так и для конструкторов. Положительно скажется ее прочтение и на уровне управления производством. Преподаватели технических университетов и колледжей могут рекомендовать ее в качестве учебного пособия по курсу "Конструирование и технология производства электронной аппаратуры".

КНИГИ

HOBSIE

- в портфеле редакции в портфеле редакции в портфеле редакции в портфеле редакции

- ➤ «Электронный нос», основанный на матрице элементарных полупроводниковых сенсоров резистивного типа. (Россия, гг. Москва, Фрязино)

- > Синтез ферромагнитных оксидов с высоким уровнем удельной электропроводности. (Украина, г. Одесса)

- ➤ Строение и высокотемпературная сверхпроводимость пленок Bi<sub>2</sub>Sr<sub>2</sub>CaCu<sub>2</sub>O<sub>3</sub>. (Россия, г. Москва)

- ➤ Дифракционная составляющая глубины резко изображаемого пространства в оптическом микроскопе. (Украина, г. Киев)

- з портфеле редакции в портфеле редакции в портфеле редакции в портфеле редакции